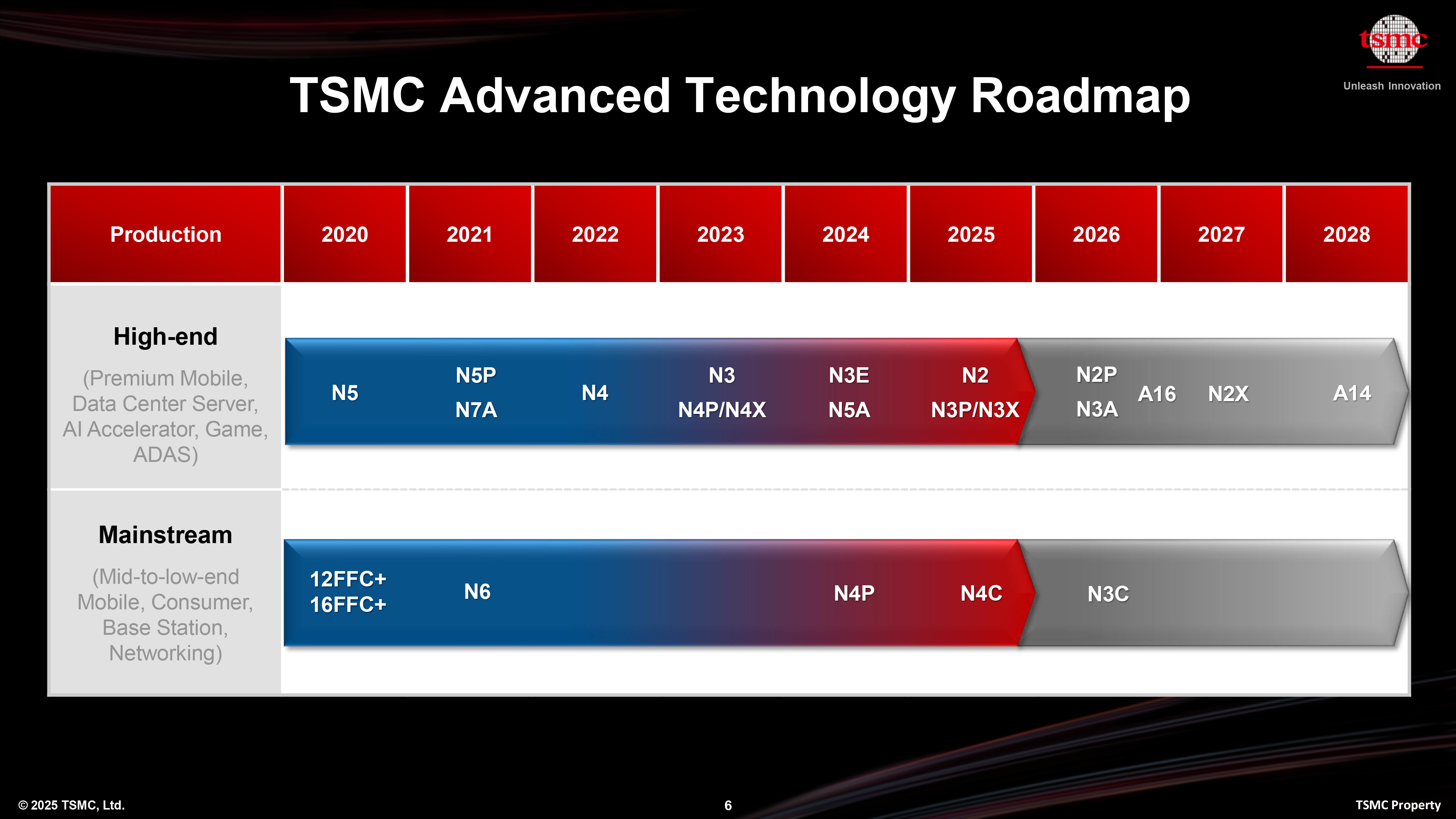

TSMC heeft zijn A14 (1.4nm-klasse) productietechnologie onthuld, waarvan het belooft dat het aanzienlijke prestaties, kracht en transistortichtheidsuitkeringen zal bieden ten opzichte van zijn N2 (2nm) proces. Tijdens zijn North American Technology Symposium 2025 op woensdag heeft het bedrijf bekendgemaakt dat het nieuwe knooppunt zal vertrouwen op de 2e generatie Gate-All-Around (GAA) Nanosheet-transistors en verdere flexibiliteit zal bieden met Nanoflex Pro Technology. TSMC verwacht dat A14 de massaproductie in 2028 zal invoeren – maar zonder stroomafgifte van de achterkant. Een versie van A14 met backside power levering is gepland voor 2029.

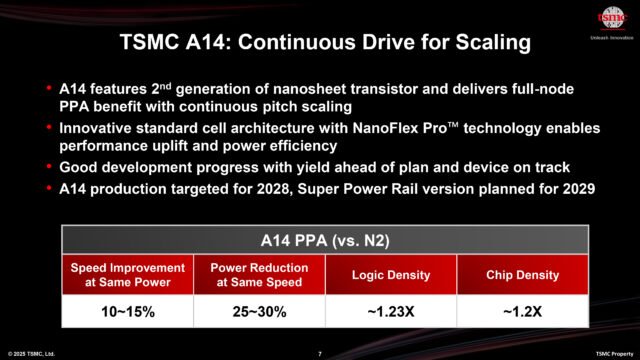

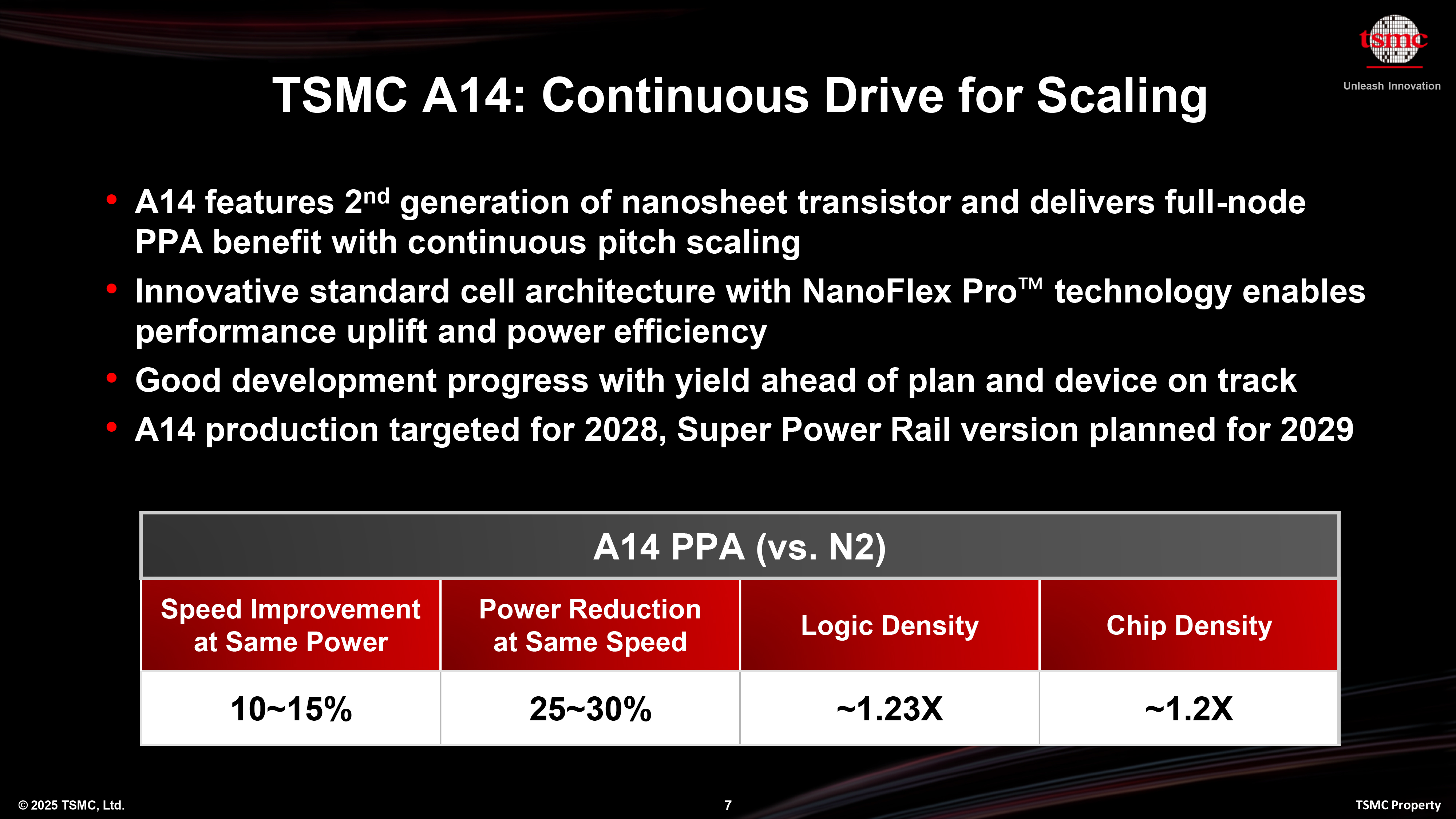

“A14 is onze full-node volgende generatie geavanceerde siliciumtechnologie”, zegt Kevin Zhang, senior vice president bedrijfsontwikkeling en wereldwijde verkoop en plaatsvervangend COO bij TSMC. “Als u naar snelheid kijkt, verbetering [compared to N2] is tot 15%, de vermogensreductie is 30%, de logische dichtheid is 1,23x de totale chipdichtheid, of ten minste 1,2x [for mixed designs]. Dus dit is een zeer, zeer substantiële technologie. “

TSMC’s A14 is gloednieuwe procestechnologie die is gebaseerd op de 2e generatie GAAFET Nanosheet-transistoren van het bedrijf en nieuwe standaardcelarchitectuur om prestaties, kracht en schaalvoordelen mogelijk te maken. TSMC verwacht dat zijn A14 een prestatieverbetering van 10% tot 15% levert bij hetzelfde vermogen en complexiteit, een 25% tot 30% lager stroomverbruik bij dezelfde frequentie en het aantal transistoren en 20% – 23% hogere transistordichtheid (voor gemengd chipontwerp en logica, vergeleken met respectievelijk N2. Aangezien A14 een geheel nieuw knooppunt is, vereist het nieuwe IP’s, optimalisaties en EDA-software dan N2P (die N2 IP gebruikt) evenals A16, die N2P is met back-side stroomafgifte.

Geadverteerde PPA -verbeteringen van de nieuwe procestechnologieën van TSMC

| Rij 0 – Cel 0 |

A16 vs N2P |

N2X vs N2P |

A14 vs N2 |

A14 SPR vs N2 |

|

Stroom |

-15% ~ -20% |

lager |

-25% ~ -30% |

lager |

|

Prestatie |

8% – 10% |

10% |

10% – 15% |

hoger |

|

Dikte* |

1.07x – 1.10x |

? |

1.2x |

dichter |

|

Transistor |

GAA |

GAA |

2e gen GAA |

2e gen GAA |

|

Power Delivery |

Spr |

Voorzijde w/ shpmim (?) |

Voorzijde w/ shpmim (?) |

Spr |

|

HVM |

H2 2026 |

2027 |

2028 |

2029 |

*Chip -dichtheid gepubliceerd door TSMC weerspiegelt ‘gemengde’ chipdichtheid bestaande uit 50% logica, 30% SRAM en 20% analoog.

** Op hetzelfde gebied.

*** met dezelfde snelheid.

In tegenstelling tot A16 (en net als N2 en N2P) mist A14 Super Power Rail (SPR) Backside Power Delivery Network (BSPDN), waarmee de technologie zich kan targeren die geen tastbare voordelen krijgen van BSPDN – die extra kosten hebben. Er zijn tal van client-, rand- en specialiteitstoepassingen die kunnen profiteren van de extra prestaties, het lagere stroomverbruik en de transistordichtheid mogelijk gemaakt door TSMC’s 2e generatie GAA nanosheet -transistoren, maar die geen dichte power bedrading nodig hebben en een traditioneel front -zij -vermogenswerknetwerk zijn.

“De technologie toont ook onze […] Nanoflex Pro Technology, [which is really] Design Technology Co-Optimization (DTCO) waardoor de ontwerper hun product op een zeer flexibele manier kan ontwerpen, hen in staat stellen om een optimaal voordeel van de stroomprestaties te bereiken, “zei Zhang.” Deze technologie gaat in productie tegen 2028. De eerste versie van deze technologie heeft niet de power rail van de achterzijde. ”

Natuurlijk begrijpt TSMC de behoeften van zijn klanten die hoogwaardige client- en datacenter-applicaties ontwikkelen, dus het is van plan A14 aan te bieden met SPR Backside Power Delivery in 2029. Voor nu heeft het bedrijf de exacte naam van de procestechnologie niet bekendgemaakt, hoewel het redelijk is om te verwachten dat het A14P wordt genoemd, de volgende TSMC’s traditionele namen. In de toekomst verwacht A14 zijn maximale prestaties (A14X) en kosten-geoptimaliseerde (A14C) versies soms na 2029.

Een van de belangrijkste voordelen van TSMC’s A14-Series Process Technologies is de Nanoflex Pro-architectuur van het bedrijf, waarmee CHIP-ontwerpers transistorconfiguraties kunnen verfijnen om optimaal vermogen, prestaties en gebied (PPA) voor specifieke toepassingen of werklast te bereiken. Met niet-Pro Finflex kunnen ontwikkelaars cellen uit verschillende bibliotheken (hoge prestaties, laag vermogen, gebiedsefficiënt) mixen en matchen binnen één blok om de prestaties, het vermogen en het gebied te optimaliseren. TSMC heeft geen expliciete technische details bekendgemaakt die nanoflex onderscheiden van Nanoflex Pro, dus we kunnen ons alleen afvragen of de nieuwe versie meer gedetailleerde bedieningselementen over cellen mogelijk maakt-of zelfs transistors-of dat het betere algoritmen en softwareverbeteringen biedt om snellere exploratie en optimalisatie van transistorniveau-afwegingen mogelijk te maken.

TSMC’s doelwit voor de productie van chips op zijn A14 -procestechnologie is 2028, hoewel het afgezien van het vermelden of het in de eerste of tweede helft van het jaar een hoge volumeproductie zou beginnen op A14. Gezien het feit dat A16 en N2P HVM in de tweede helft van 2026 (dwz eind 2026) zullen aftrappen, met chips op de markt in 2026, hebben we het gevoel dat A14 het doelwit is van de eerste helft van 2028 – op schema om klanttoepassingen te bedienen in de tweede helft van het jaar.